资讯文章

信号源内阻对差动放大电路共模抑制比的影响分析与改善方法

《差动放大电路中电阻误差对电路共模抑制比的影响与蒙特卡洛分析》一文,介绍在差动放大电路设计时匹配电阻精度造成的影响,而在差动放大电路应用中还有一个不可忽略的因素——信号源内阻。本篇对信号源内阻在差动放大电路的共模抑制比影响进行理论分析,并提供改善方法,同时结合仿真验证。

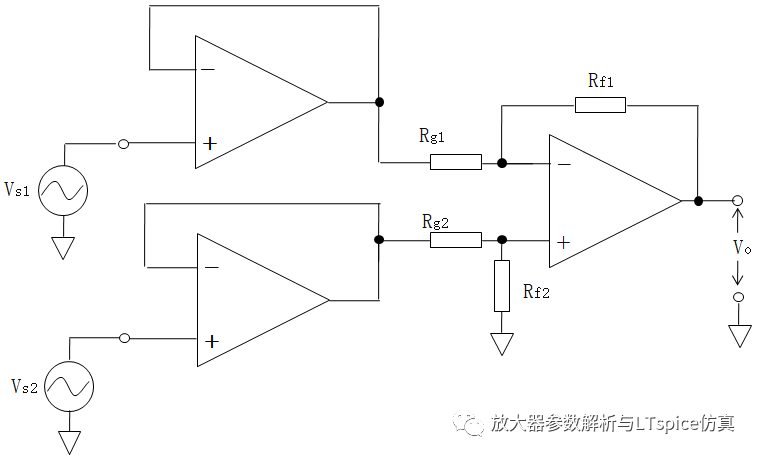

如图2.54,将Rg1与Rg2值设定为Rg,Rf1与Rf2值设定为Rf,电路差模增益Ad(常态增益ANF)为Rf比Rg。当考虑信号源的输入阻抗因素时,电路实际的输出电压应由ANF-、ANF+决定,二者满足式2-34、2-35。

图2.54差分放大电路的信号源阻抗分析

假定信号源内阻Rs1、Rs2远小于Rg与Rf之和,电路的共模抑制比为式2-36

由式2-36可知,当信号源内阻Rs1与Rs2的差值与Rg比值占1%时,ANF为1时,电路的共模抑制比仅仅为40dB,即误差为1%级别。

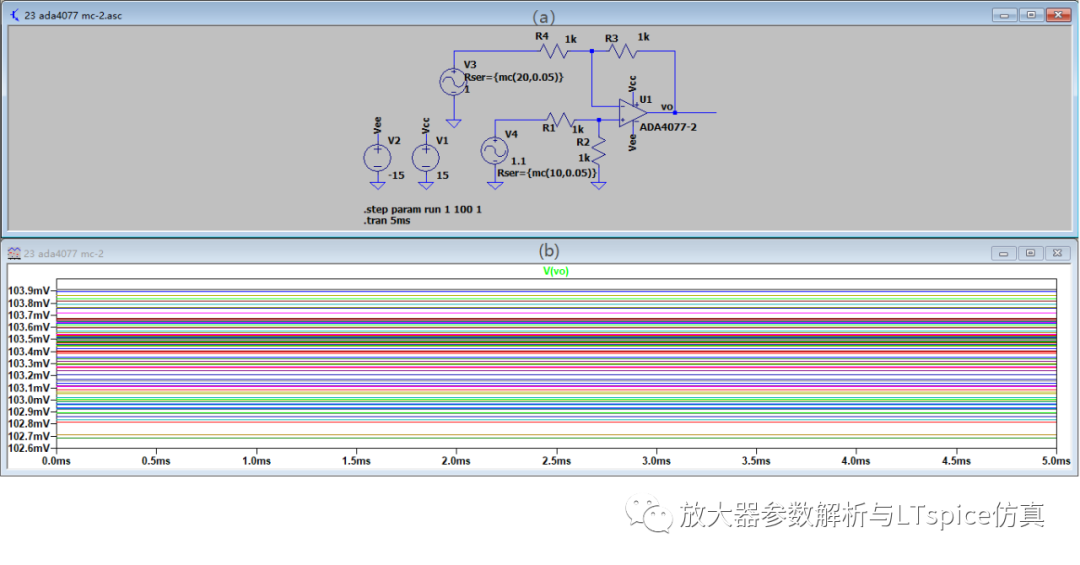

如图1(a), 使用ADA4077组建增益为1倍的差动放大电路,R1~R4阻值为1KΩ,V3是具有20Ω内阻,输出1V 直流信号的信号源,V4是具有10Ω内阻,输出1.1V 直流信号的信号源。另外,设定V3,V4内阻的精度为5%(模拟信号源内阻因环境的变换)。

该电路理想情况下,会将输入V3与V4的差模信号转化为100mV输出,使用模特卡洛分析的结果如图1(b),可以清晰看到输出信号最大值为103.9mV,最小值为102.7mV, 均值的103.3mV,输出的误差为3.3%左右,符合上述分析。

图1 信号源内阻对ADA4077差动电路影响

分析式2-36,降低信号源内阻之差,可以提高电路的共模抑制,而降低信号源内阻影响的方式为增加放大器的输入阻抗。但是直接增大Rg,Rf,随工作温度上升由温漂带来的失调电压也会随之增大。所以有效降低信号源内阻影响的方式,是使用两个放大器作为输入缓冲器提高输入阻抗,如图2.55,改善后的差动电路与信号源构建系统的共模抑制比仅由的Rg1、Rg2、Rf1、Rf2的误差δ决定,应避免出现《放大器共模抑制比(CMRR)参数评估与电路共模抑制能力实例分析》中错误示例的匹配电阻配置。

图2.55 高输入阻抗差动电路

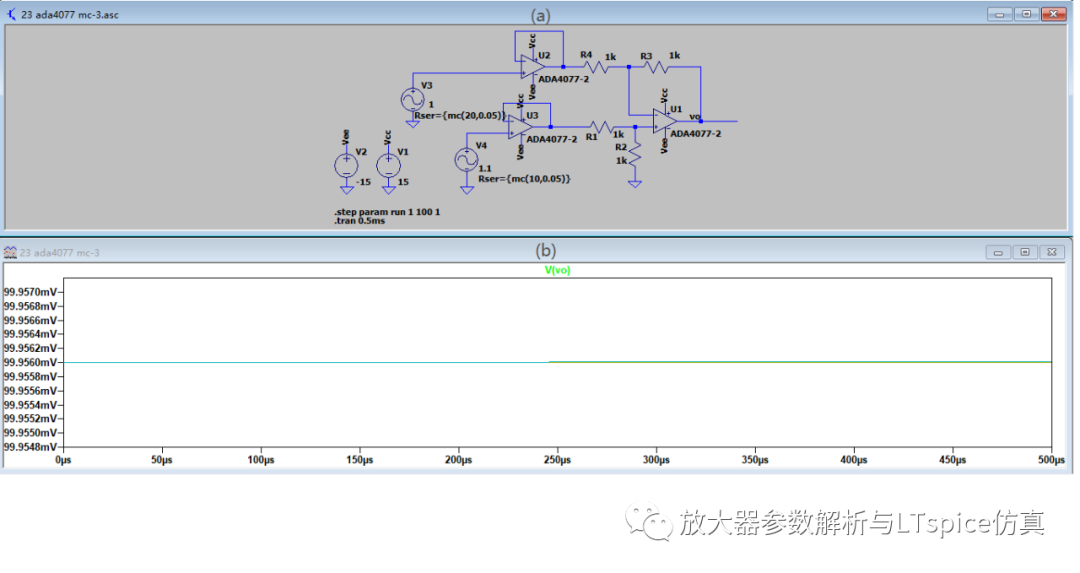

在将图1(a)中,V3,V4信号源输出与ADA4077差动放大电路之间串入缓冲器电路,得到图2(a),保留V3,V4内阻阻值误差为5%的条件,再次进行蒙特卡洛分析的结果如图2(b)。

1.改善电路相比缺少缓冲器的电路,误差提升为0.044%;

2.内阻阻值的变化不会导致输出误差。

图2 信号源内阻对ADA4077差动改善电路影响

综上,在实际的差动电路应用中,输入信号源内阻的绝对阻值、以及相对变化不容忽略,需要在输入级增加缓冲器电路提高电路的精度。来自:F放大器参数解析

声明:本文内容由易百纳平台入驻作者撰写,文章观点仅代表作者本人,不代表易百纳立场。如有内容侵权或者其他问题,请联系本站进行删除。

红包

6

7

评论

打赏

- 分享

- 举报

评论

0个

手气红包

暂无数据

暂无数据相关专栏

-

浏览量:3328次2020-11-28 09:22:35

-

浏览量:3026次2020-11-24 10:13:18

-

浏览量:3800次2020-07-15 13:45:57

-

浏览量:18546次2021-06-15 00:09:06

-

浏览量:3919次2019-10-23 16:13:13

-

浏览量:1821次2019-02-26 16:42:37

-

浏览量:1839次2019-11-07 08:57:36

-

浏览量:2264次2020-07-28 17:27:40

-

浏览量:2904次2019-11-27 09:37:44

-

浏览量:2478次2020-07-22 14:39:14

-

浏览量:21069次2021-06-20 17:47:13

-

浏览量:1924次2019-10-24 17:44:40

-

浏览量:2576次2020-07-15 18:52:03

-

浏览量:2855次2020-07-22 14:25:03

-

浏览量:13476次2020-12-08 20:25:24

-

浏览量:2350次2022-03-30 17:15:07

-

浏览量:4851次2020-12-04 10:33:46

-

浏览量:1978次2018-04-19 11:22:23

-

浏览量:4827次2019-10-11 09:26:12

置顶时间设置

结束时间

删除原因

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

打赏作者

易百纳技术社区

您的支持将鼓励我继续创作!

打赏金额:

¥1

¥5

¥10

¥50

¥100

支付方式:

微信支付

微信支付

举报反馈

举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

审核成功

发布时间设置

发布时间:

请选择发布时间设置

是否关联周任务-专栏模块

审核失败

失败原因

请选择失败原因

备注

请输入备注

微信扫码分享

微信扫码分享 QQ好友

QQ好友