SmartNIC 架构:向加速器转型以及 FPGA 占据主导地位的理由

与普通 NIC 相比,SmartNIC 整合了更多的计算资源。但是这些架构就像雪花一样各不相同,因此我们将深入研究规模最大、最受欢迎的供应商所提供的几种方法。

正文:

普通网络接口卡 (NIC) 是围绕单独的专用集成电路 (ASIC) 构建的,该集成电路被设计成以太网控制器。这方面的典型示例包括迈络思的 ConnectX 系列、博通的 NetXtreme 以及赛灵思的 XtremeScale。通常,这些芯片会围绕第二个设计目标进行进一步优化;例如,ConnectX 系列也支持 Infiniband,而 XtremeScale 则专注于内核旁路。这些控制器在既定功能方面表现优异,代表着行业最佳水准,但它们并不是 SmartNIC。

在本文中,我们将 SmartNIC 定义为 NIC,它允许在购买后的某个时刻将附加软件加载到 NIC 中,用于添加新功能或支持其他功能。这在很大程度上类似于您所购买的智能手机,然后从该供应商的应用商店安装应用。

能够将未来的代码加载到 NIC 是 SmartNIC 的必备功能,它要求更强的计算能力和更大的板载存储器,这是普通 NIC 所不具备的特性。大多数 SmartNIC 方法都是从基本的以太网控制器开始,要么在芯片上作为固件,要么在适配器上作为单独的芯片。也可以使用下列三种方法之一,通过提升其计算能力,实现普通 NIC 的智能化:

- 大量 Arm 核心集成,也称为集群或网格、块。

- 流处理核心 (FPC),属于定制设计网络处理器,通常是 P4。

- 现场可编程门阵列 (FPGA),可编程逻辑。

许多 SmartNIC 通常使用一个或多个 Arm 核心来管理 NIC 中的控制平面。有些甚至允许将修改过的 Linux 内核加载到一个或多个核心中。这些 Arm 核心通常负责将代码加载到其他处理元件中,收集统计信息和日志,并监视 SmartNIC 的运行状况和配置。它们不会接触任何网络数据包,并且通常会“带外”运行,这意味着它们无法通过“常规”网络接口或 PCIe 命令进行访问。

此外,他们应该只能通过先前受保护的接口接受经过正式签署的固件包。除了架构草图以外,我们不会在下面调用这些控制平面的 Arm 核心,因为它们需要管道,而且它们本身通常不会为 SmartNIC 提供的特性集增加价值。

产品比较

为了理解 SmartNIC 与普通 NIC 的不同之处,我们需要深入了解全球四大 NIC 公司以及两家初创企业推出的 SmartNIC 产品,看看他们做出了哪些改进。入选的六家公司分别是英特尔、博通、英伟达(前身为迈络思)、赛灵思、Netronome 和 Pensando。此外,我们还将对目前被称为 Fungible 的隐形项目提出一些见解。

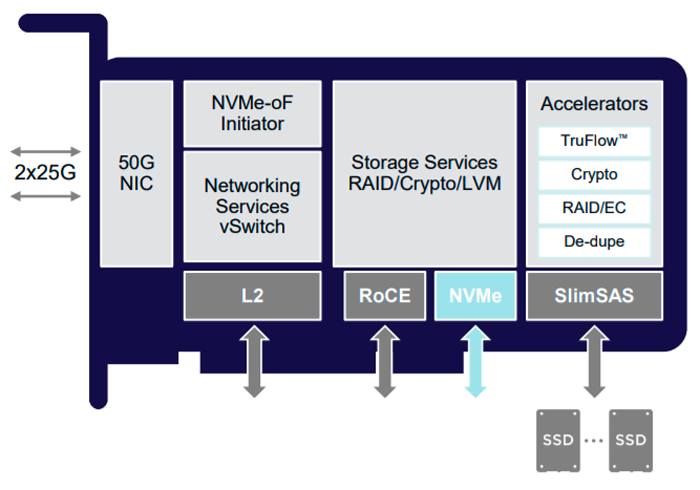

博通

博通是以太网 NIC 控制器商品市场上无可争议的领导者。因此当博通装配其 Stingray SmartNIC 并加入竞争时,博通采用了单芯片方法(图 1)。与其他竞争对手的众多芯片板相比,单芯片 SmartNIC 解决方案的板级生产成本始终保持在较低水平。

1.所示为博通在 2019 SDC 大会上揭晓的 Stingray 架构

博通以 NetXtreme E 系列控制器的逻辑为基础,设计了位于 Stingray 核心的 NetXtreme-S BCM58800 芯片。然后,他们在集群配置中部署了主频为 3Ghz 的 8 个 Arm v8 A72 核心。运行在 3GHz 下的这些核心可谓是速度最快的 SmartNIC Arm 核心。此外,经过配置,Stingray 可使用高达 16GB 的 DDR4 存储器。接下来,他们加入了一些逻辑,以最高 90Gb/s 的速度卸载加密,同时卸载擦除编码和 RAID 等存储处理。

最后,博通还采用了其带有一些神秘色彩的 TruFlow 技术。这是一个可配置的流加速器,用于将常见的网络流过程转移到硬件中。我们认为博通在使用 P4 处理器。这样可以释放 Arm 核心,用于集中处理流层面和数据包层面的计算密集型任务。从发布的内容来看,TruFlow 能够在硬件中分担像 Open vSwitch (OvS) 这样的任务。此外,博通还声称 TruFlow 在硬件中实现了众多经典的软件定义网络 (SDN) 概念,例如分类、匹配和操作。因此,Stingray 配备了两个可编程组件,即 TruFlow 和一个由四个 3Ghz 双核 Arm v8 A72 复合体组成的集群。

博通拟在今年夏末将 Stingray 升级到 7nm 工艺,从而将核心数从 8 个增加到 12 个。了解到他们所提供的产品的复杂性,博通为 SmartNIC 应用开发和存储控制器开发提供了 Stingray 开发套件。虽然这并不是常规做法,但对于完整的 SmartNIC 产品解决方案来说,是必要的组成部分。

英伟达

英伟达开发的图形处理单元 (GPU) 已成为高性能计算 (HPC) 加速器的不二之选。今年年初,英伟达最终以 70 亿美元的价格完成了对迈络思的收购。为了占领 HPC 市场,英伟达选择了领先的无限带宽技术互联供应商,以便为 HPC 客户提供完整的解决方案。这与克雷过去的做法非常相似。

英伟达最近还收购了 Cumulus Networks,后者是开源以太网交换机操作系统的领导者。显而易见的是,软件一直是迈络思的弱点,英伟达很早就意识到了这一点。关于 SmartNIC,英伟达还通过收购迈络思得到了一个意外惊喜。

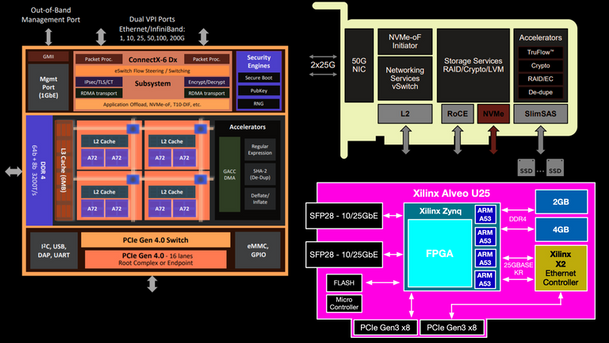

迈络思是最早进入 SmartNIC 领域的公司之一,但这是通过收购实现的。他们当前的 Bluefield 2 解决方案(图 2)是在 2015 年通过收购 EZchip 收购 Tilera 而完成构建的。Tilera 拥有首个申请知识产权的高度并行 SmartNIC 实现方案,它是从更早的 MIT 研究项目逐步发展起来的。

2.产品数据手册中的 Mellanox 的 Bluefield 2 架构

Tilera 将处理核心作为芯片上的块进行排列,每个核心都有一条高速总线连接到周围的四个核心。他们的旗舰产品早在 2013 年就可支持多达 72 个 MIPS 核心、存储器控制器、加密模块、PCIe 块和 mPipe,以及一种使用 SFP+连接器对外连接多个 MAC 的通道集合。迈络思通过用 Arm 替换核心并将 mPipe 换成 ConnectX 逻辑来推进这一进程。目前采用 8 个 Arm v8 A72 核心,核心数与博通一样,但时钟频率仅有 2.4GHz。这些核心被排列成由四个双核 Arm 构成的集群。Bluefield 目前正在使用 Avago 16nm 工艺。但与博通如出一辙,它也准备在今年夏天采用 7nm 工艺,并将核心数从 8 个增加到 12 个。

虽然这种方法与博通 Stingray 非常类似,但它欠缺构成博通架构核心的并行 P4 处理器。P4 是每家公司的目标,只不过并不是每家公司都对此公开表明。下面提到的博通、赛灵思和 Pensando 都很关注 P4。这也是 Cumulus Networks 的用武之地,他们在 P4 编程方面有着丰富的经验。因此,为了向未来的 Bluefield 产品系列提供前端服务,英伟达设计了 P4 数据包处理引擎也就不足为奇了。

Pensando

这家最新加入竞争的 SmartNIC 初创企业 Pensando 由 Mario Mazzola(董事会副董事长)、Prem Jain(首席执行官)、Luca Cafiero(董事会成员兼技术顾问)和 Luca Cafiero(首席业务官)组成的“MPLS”团队共同创立。这个工程团队曾在思科系统 (Cisco Systems) 引领其数项关键技术的开发,成立过四家被思科收购的初创企业。思科前首席执行官 John Chambers 任董事会董事长。

鉴于所创立的团队以及董事会董事长的声望和过往经验,普遍共识是 Pensando 会率先通过一些固定客户证明其技术的有效性,然后打包出售给思科。思科掌握一些通用的 NIC 技术并运行着几个内部 SmartNIC 项目。但据说这些项目的进展并不顺利。因此,Pensando 显然有望填补这一空白。

Pensando 最初提供两种产品,但近期缩减到一个产品,即 DSC-25“分布式服务卡”,这个甚至听名字就像是思科产品。这是一款单一的 P4 处理器芯片,使用一个 Arm 核心负责部分辅助处理。根据产品数据手册,两个处理器都可支持高达 4GB 的板载存储器(图3)。

3.Pensando DPU 架构(来自 2020 年 2 月 24 日发表的 P4.org 博文)

这款称为 Capri 的处理器是一个拥有多个并行级的 P4 可编程单元;但是具体的并行处理程度未知,因为数据包性能、时延和抖动等尚未披露。由于缓存未命中而导致的指令内存提取会影响所有指标的性能,所以 Pensando 妥善管控 P4 应用,将它们保留在 Capri 缓存中。其他被称为服务处理卸载 (Service Processing Offloads) 的计算单元则负责处理加密、存储流程和其他任务。Pensando 声称 Capri 能够提供线速性能。

Netronome

Netronome 是这个领域里颇有年限的初创企业,2003 年就已开业,到目前已经历五轮总计 7,300 万美元的融资。该公司自 2015 年开始积极推广 P4,并在当年演示其首款使用该技术的 SmartNIC。自从那时起,Netronome 赢得长足发展,但近期有消息称其发展不利,可能会退出市场。

图 4 所示的是 Netronome 当前的 NFP4000 流处理器架构。未使用单个 P4 处理引擎,该公司使用两种级别的可编程核心:48 个数据包处理核心和 60 个流处理核心。其余芯片专门负责分类、修改和管理。所有这些核心都可以在 P4 中进行编程。

4. Netronome 的 FP4000 流处理器架构

最终,Netronome 声称这些核心能在线速下保持单链路 100-Gb/p 的速度,每秒处理 1.48 亿个数据包,数百万个完全匹配流和通配符流。此外,它们还支持要求封装的 10 万个以上的隧道连接。该技术支持的目标应用种类繁多,包括入侵检测系统 (IDS)、入侵防护系统 (IPS)、新一代防火墙 (NGFW)、路由器、负载均衡器、数据包代理、SDN、NFV 和大量其他应用。

Fungible

Fungible 是一家长期耕耘 P4 领域,但尚未展露头角的颇具潜力的后起之秀。在经历三轮总计近 3 亿美元的融资后(其中 2 亿美元来自去年的 C 轮融资,由软银愿景基金提供),Fungible 宣布即将推出一款产品。目前该公司有 180 名员工,没有产品,没有收入,也没有可见客户。

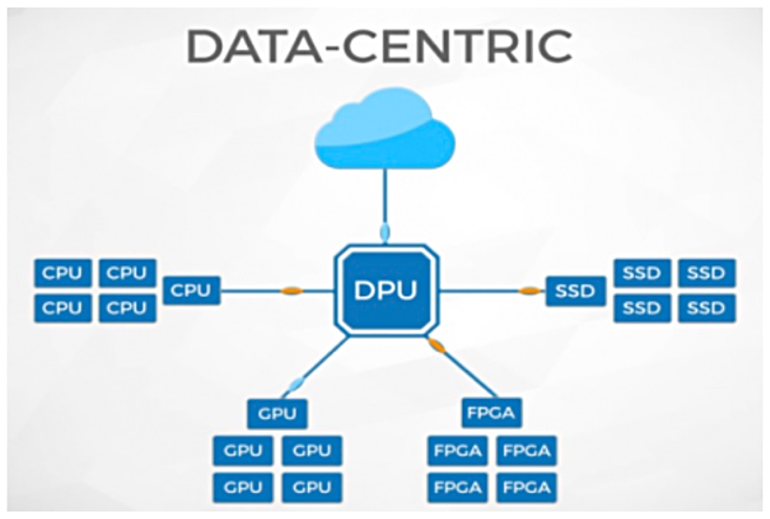

Fungible 声称将生产一款数据处理单元 (DPU),但实际架构和组成尚未可知。Fungible 提供了如图 5 所示的原理图,但如同架构图不具备重要意义一样没有突出重点。很多文章都提到他们的产品将在今年夏天发布,因此我想提醒大家关注这家公司。

5. Fungible 高级架构(摘自 2020 年 2 月 11 日 BlocksAndFiles.com 博文发帖)

他们的创始人之一兼首席架构师是曾在 Chelsio Communications 积累了 10 年经验的资深人士,专门从事以存储为中心的以太网 NIC 方面的研究。此外,他们的软件和固件工程副总裁也曾在 Chelsio 任职,而且他的工作经验有 13 年之久。因此,尽管 Chelsio 过去的核心产品是 ASIC,但如今从头开始生产一款领先的 SmartNIC 以太网控制器 ASIC 很容易就会消耗掉他们超过 5000 万美元的宝贵资本。

有人推测,他们将采取阻力最小的方法来获得收益,并利用 FPGA 平台开发他们的初始产品,同时将特有的 ASIC 设计加载到该平台。随后,他们可以在开始追求客户和收益的同时推出设计方案。将设计加载到 FPGA 中有助于 Fungible 轻松地修复设计缺陷,并可以根据客户要求快速改善。如今,FPGA 的应用越来越广泛,我们已经开始看到像 RISC-V 这样成熟的处理器架构被加载到这些平台上。

英特尔

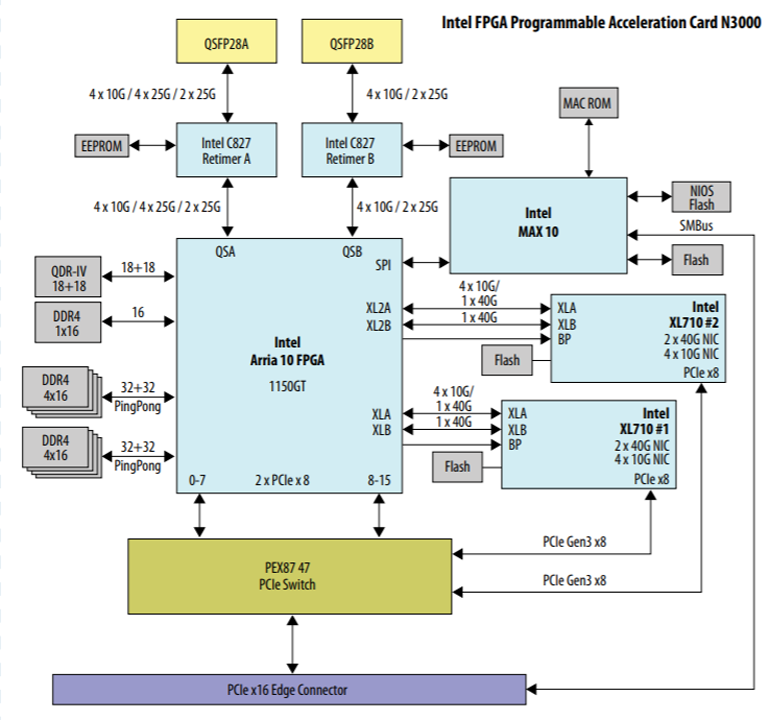

说到芯片公司,英特尔是当之无愧的行业之首。十多年来,英特尔一直持续不断地推出一系列高性能 10GbE 控制器。其 XL710 平台出货量已有数百万件,是众多数据中心服务器的必备产品。

对于其新款N3000 SmartNIC,英特尔采用了五种芯片完成电路板开发(图 6)。这种方法成本很高,因为大多数厂商都在努力完成单芯片设计。英特尔还将一对 XL710 以太网控制器和一个使用 48 通道的第三代 PEX8747 PCIe 交换芯片的 Arria 10 FPGA 融合在一起。每个 XL710 有 8 个通道,Arria 有 16 个通道,PCIe 插槽有 16 个通道。第五块芯片是用于管理 FPGA 的 MAX 10 FPGA 基板管理控制器(BMC),就像在其他 SmartNIC 上使用 Arm 核心来处理控制平面管理一样。

6.英特尔 N3000 SmartNIC 架构图示(摘自产品数据手册)

该电路板有两个直接连接到 FPGA 的 QSFP28 端口。然后 8 条 10G 通道将 FPGA 留给每个 XL710。这是一种典型的无缝嵌入方法,它使 FPGA 能够在数据包被传递到 XL710 之前处理数据包。

使用现成的以太网控制器和 FPGA 构建 NIC 并不是什么新鲜事。早在 2012 年,Solarflare Communications 就在 NIC 的两个 QSFP 端口与其以太网控制器之间放置了一个 FPGA,用于创建其应用加载引擎 (AOE) 平台。这是上述英特尔 N3000 设计的先驱,它使 Solarflare 为金融客户提供了令人印象深刻的即时交易结果,耗时仅为 350ns。8 年后的今天,该记录为 24.2nm。

英特尔的方法支持 FPGA 在 XL710 之前进行数据包处理。英特尔的 FPGA 具有 115 万个可编程逻辑单元和两个 4GB 的 DDR4 存储器组,这为它处理以下 SmartNIC 任务提供了充足的空间:

- 虚拟宽带网络网关 (vBNG)

- 层级服务质量 (HQoS)

- 数据包分类、监控、调度和成形

- 虚拟化演进分组核心 (vEPC)

- 5G 新一代核心网络 (NGCN)

- 互联网协议安全 (IPSec)

- IPv6 分段路由 (SRv6)

- 矢量数据包处理 (VPP)

- 虚拟无线电接入网 (vRAN)

尽管英特尔已将上述工作负载用于其 N3000 平台,但目前还不清楚他们是否已交付所有必要的软件来卸载该 SmartNIC 上的每个应用。SmartNIC 的消费者会发现,软件才是症结所在,所有这些公司在硬件方面都很出色,但是软件交付又完全是另一回事。

赛灵思

SmartNIC 领域中另一家杰出的 FPGA 供应商是赛灵思,它是上世纪 80 年代中期首家实现 FPGA 商业化的公司。现如今,赛灵思已经是 FPGA 领域的霸主,英特尔则被远远地甩在后面。赛灵思于 2019 年秋季收购了 Solarflare Communications,自 2012 年以来,Solarflare 一直在为电子交易构建基于 ASIC 和 FPGA 的 NIC。来自英国剑桥的 Solarflare 工程团队是赛灵思 Alveo U25 SmartNIC 的研发主力(图 7)。赛灵思的成功得益于 Solarflare工程团队在这个市场积累的十多年的经验。

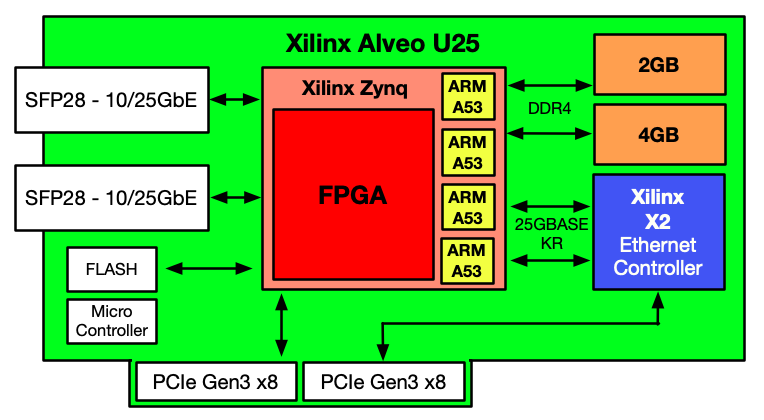

7.赛灵思 Alveo U25 架构原理图。(来源:赛灵思)

Alveo U25 将双 SFP28 端口直接连接到 Zynq 系列芯片。Zynq 实际上是一种片上系统 (SoC),因为它不仅包括 FPGA,还包括用于数据包处理的四核 Arm A53。然后,Zynq 通过第三代 PCIe 提供的 8 个通道直接连接到主机服务器,或是通过 SerDes 连接到 X2 以太网控制器芯片,后者也可以通过第三代 PCIe 8 个通道连接到主机。这种方法使得 Zynq 能够在数据包被传递到 X2 芯片之前对其进行处理,或者完全绕过 X2 芯片。

此外,U25 还包括 6GB 的 DDR4 存储器,可以通过运行在该芯片上的程序访问 Zynq 的 FPGA 和 Arm 核心。FPGA 具有 52 万个逻辑单元,但是提供的四核 Arm 足以弥补减少的可用门数。

赛灵思将 U25 推向市场,最初是为了满足那些需要开放虚拟交换机 (OvS) 卸载功能的客户。赛灵思已经宣布,在不久的将来,他们将增加 IPSec、机器学习 (ML)、深度包检测 (DPI)、视频转码和分析的卸载数量。赛灵思也许是 SmartNIC 领域中发展最为全面的企业。两年前,在收购 Solarflare 的准备阶段,他们是合作伙伴,并在 OCP 峰会上公开展示了 X2 控制器逻辑作为软 NIC 在更大型 FPGA 中的运行情况。

像英特尔一样,赛灵思也拥有数条计算芯片产品线:Kintex、Virtex、Zynq 和 Versal。Kintex 和 Virtex 都是纯 FPGA,该产品线中的部分型号拥有近 300 万个逻辑单元,几乎是英特尔在其 N3000 中使用数量的三倍。此外,赛灵思还通过硅中介层创造了奇迹,并在 Virtex 芯片上分层放置了高达 16GB 的高带宽存储器 (HBM)。所有四条芯片生产线的其他芯片也采用了这项技术。

Zynq 是他们的 SoC 芯片系列,包括 FPGA 可编程逻辑、四核 Arm、实时 Arm 核心、DDR 控制器以及用于以太网和 PCI Express 的连接逻辑。Versal 超越了 SoC,成为一个基于 7nm 芯片技术的自适应计算加速平台 (ACAP)。ACAP 通过添加数百个人工智能 (AI) 核心和数字信号处理 (DSP) 引擎来扩展 Zynq 架构。AI 核心在某种程度上是新器件,但它们在本质上属于单精度计算引擎。最终,赛灵思将把他们公开展示的 SoftNIC 与 Versal 结合起来。

SmartNIC 的当前状况

正如我们在 Netronome 身上,甚至是 Solarflare Communications 身上看到的,SmartNIC 已有长期发展历程。谷歌、亚马逊为代表的潜在大客户已从该市场抽身,自己设计和构建其内部解决方案。与此同时,Facebook、微软均已开始提供高级架构,此后,行业供应商纷纷涌向该架构。

就在这一切开始变得有序的时候,SoC、更重要的是 FPGA 已日臻成熟,足以担当 SmartNIC 的基础技术。十年前,硬件加速技术的第一波冲击袭来,业界开始沉浸在 GPU 产品的大潮中。现在,随着 FPGA 容量突破 300 万个逻辑单元,我们正将 FPGA 与其他可组合的处理模块结合,用于网络、内存、存储和计算。这里的计算指的是通过 SoC 块甚至是 ACAP 实现片上核心集群。

随着技术不断发展,硬件加速的第二波浪潮正在形成。GPU 需要新的编程 API 和工具来支持一些平台,FPGA 同样如此。然而差异在于,FPGA 技术已持续演进发展超过 35 年,它的时代正在到来。随着 SmartNIC 市场的最终崛起,它将与下一波基于 FPGA 的硬件加速器相融合。这将在加速市场上平添多种类型的解决方案。一场剧变也许就此展开,并改变我们未来的计算观。

SmartNIC 正推动计算能力逐渐扩展到网络边缘,从而释放服务器 CPU 来处理更多复杂的业务关键型任务。研究表明,在高度虚拟化的环境中,网络可以消耗主机 CPU 周期的多达 30% 来处理 OvS 事务等任务。

试想一下,是否可以在SmartNIC中完成存储功能、加密、DPI和复杂的路由?这可能会将通常用以处理这些工作负载的大比重CPU周期交付回主机CPU。

为了保持领先地位,Pensando 和 Fungible 为代表的新兴公司持续为 SmartNIC 市场注入创新特性和功能。与此同时,赛灵思、英特尔、博通和英伟达等技术领先企业也纷纷着手改进基础计算核心和专用 P4 处理引擎。激动人心的时刻即将来临。

来源:XILINX

- 分享

- 举报

暂无数据

暂无数据-

浏览量:2211次2018-04-16 21:28:57

-

浏览量:2187次2018-08-09 09:27:13

-

浏览量:3023次2020-10-10 09:40:22

-

浏览量:3305次2020-10-26 10:42:02

-

浏览量:7484次2022-05-11 08:10:28

-

浏览量:2090次2022-09-26 15:03:03

-

浏览量:4919次2021-03-23 15:16:56

-

浏览量:2201次2022-01-15 09:00:26

-

浏览量:7461次2020-12-09 09:43:15

-

浏览量:1762次2020-02-04 15:21:25

-

浏览量:1651次2022-01-12 09:00:13

-

浏览量:3917次2022-03-02 09:00:13

-

浏览量:2632次2019-12-26 15:22:22

-

浏览量:1882次2022-01-14 09:00:21

-

浏览量:3795次2020-10-16 10:59:27

-

浏览量:1736次2020-07-02 16:11:35

-

浏览量:2677次2019-07-02 14:31:20

-

浏览量:3432次2022-03-20 09:01:41

-

浏览量:2655次2020-10-22 11:24:10

- 12G-SDI高清视频开发案例,让4K视频采集更便捷!基于Xilinx MPSoC高性能平台

- 借助ROS 2实现软件定义自适应机器人

- FPGA的设计艺术(1)FPGA的硬件架构

- 高速计算新体验:Xilinx Virtex UltraScale+ FPGA 新添独一无二高速新成员

- FPGA的设计艺术(21)Verilog中如何对组合逻辑进行建模?

- 突破软硬壁垒,解锁全员创新 —— Xilinx 隆重发布 Vitis 统一软件平台

- 【转载】Versal家族到底都有哪些兄弟姐妹

- 不差钱的话,您会用激光雷达吗?

- 探索高性能 5G 无线方案

- FPGA逻辑设计回顾(5)多比特信号的CDC处理方式之MUX同步器

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

易百纳技术社区

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友