用于扇出型晶圆级封装的铜电沉积

随着集成电路设计师将更复杂的功能嵌入更狭小的空间,异构集成包括器件的3D堆叠已成为混合与连接各种功能技术的一种更为实用且经济的方式。作为异构集成平台之一,高密度扇出型晶圆级封装技术正获得越来越多的认可。此种封装解决方案的主要优势在于其封装的基片更少,热阻更低,电气性能也更优秀。这是一个体现“超越摩尔定律”的例子,即使用 “摩尔定律”以外的技术也能实现更高的集成度和经济效益。

异构集成技术

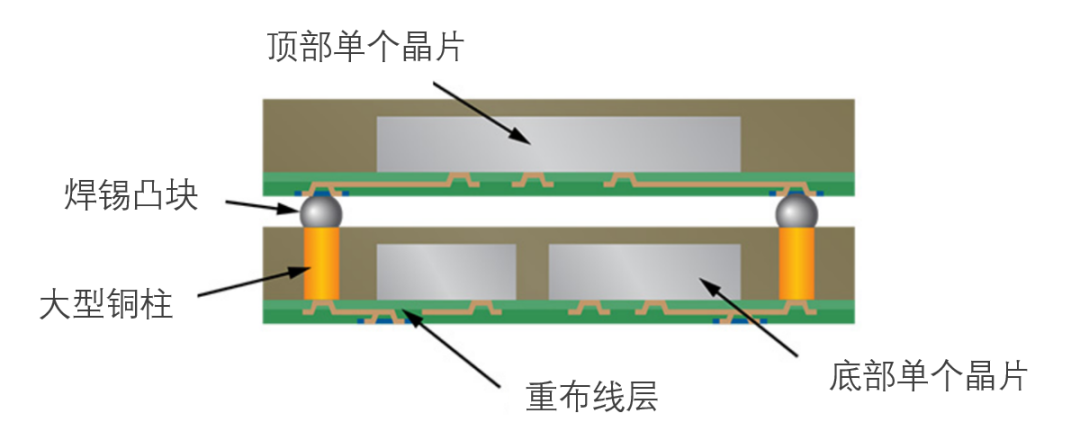

高密度扇出型封装技术满足了移动手机封装的外形尺寸与性能要求,因此获得了技术界的广泛关注。构成此技术的关键元素包括重布线层(RDL)金属与大型铜柱镀层。重布线层连通了硅芯片上的高密度连接和印制电路板的低密度连接。通常需要使用多层重布线层,才能够让信号路由至电路板。

如图1所示,大型铜柱是垂直连接不同层级的金属支柱。顶部单个晶片的焊锡凸块被放置于大型铜柱之上,并通过回流焊完成连接。

图1. 2.5D封装中的中介层结构

大型铜柱的工艺挑战

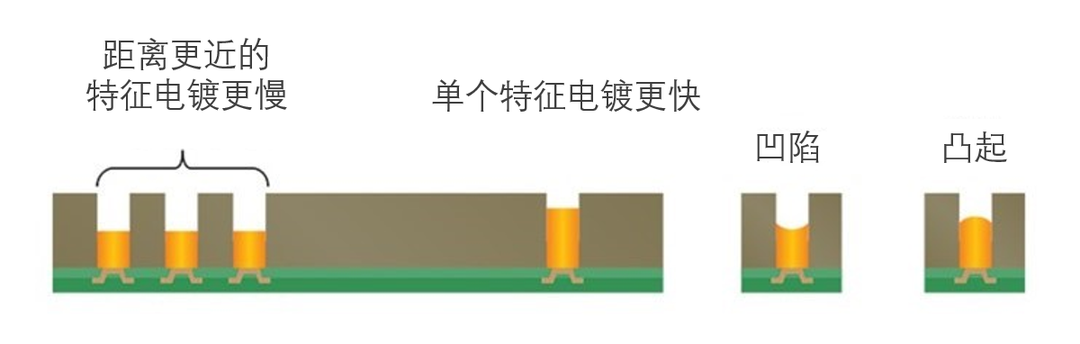

大型铜柱的区别在于其尺寸大小:它的高度和宽度是标准铜柱的5倍之多。构建大型铜柱的传统方法是采用常规电镀,这个过程漫长且缓慢。而最大的问题在于,此过程通常会产生不可接受的不一致结果。电镀铜柱的高度会随局部电流负载密度的不同而变化,并可能在支柱顶部产生一定程度的隆起或凹陷,而不是所需的平坦表面(图2)。这种高度与特征形状的不一致,可能会需要额外的后续平面化步骤(如CMP),并会导致连接不稳定,降低设备性能,增加总体工艺时间和成本。

影响以上电镀结果的单个晶片布局差异包括特征形状、宽度、深宽比以及周围光阻的厚度和给定区域的特征密度。这些差异可能会演变成为晶圆、单个晶片或各个特征之间的差异。

解决这个问题的方法之一就是在目标厚度上电镀多余的金属,然后逆转电镀极化与电流方向。这将回蚀所添加金属,以缩小铜柱的高度分布,或使大型铜柱的顶部更平整。但这种方法可能无法有效提升不同长度铜柱尺寸的一致性,而且通常会导致不良变形,使得大型铜柱的表面粗糙凹陷,边缘腐蚀。

图2. 电镀大型铜柱的常见差异包括电流负载问题、凹陷和凸起

泛林集团的解决方案

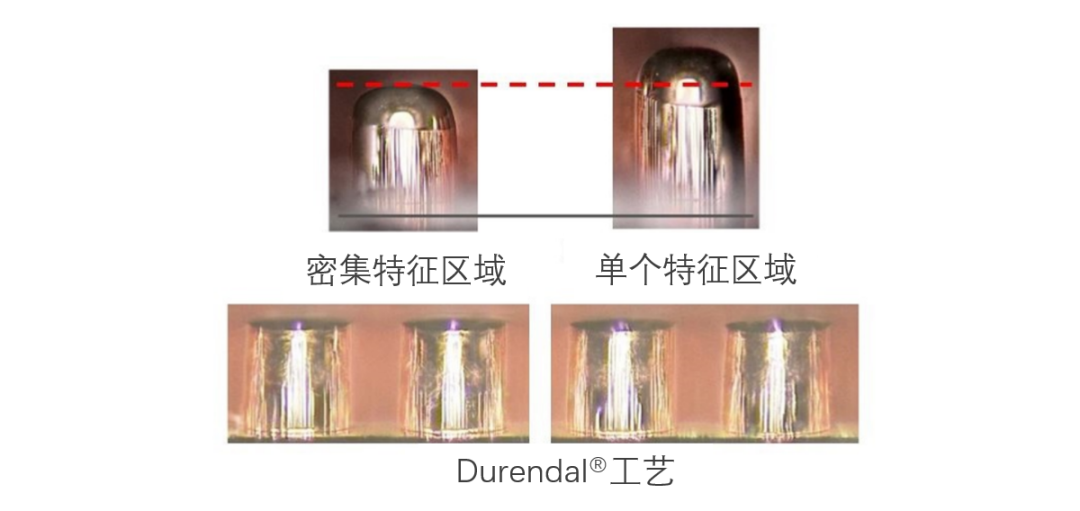

泛林集团通过其独有的Durendal®工艺解决这一问题。该工艺可以产出优质、光滑的大型铜柱顶部表面,整个晶圆上的大型铜柱高度也非常均匀。整套Durendal®工艺可以在SABRE® 3D设备上实施完成。

图3. 通过SABRE® 3D使用Durendal®工艺,产出尺寸均匀、高质量的大型铜柱。下方的图片比较了晶圆边缘(左侧)与晶圆中心(右侧)大型铜柱的高度差异。

Durendal®工艺提供了一种经济高效的方式进行单个晶片堆叠,并能产出高良率以及稳固可靠的连接。在未来,我们期待Durendal®工艺能促进扇出型晶圆级封装在单个晶片堆叠中得到更广泛的应用。

声明:本文出自公众号【 泛林半导体设备技术】,版权归原作者所有,转载请注明出处。

- 分享

- 举报

暂无数据

暂无数据-

浏览量:1676次2023-04-19 09:14:58

-

浏览量:3080次2020-12-12 09:53:13

-

浏览量:2892次2020-11-24 10:36:04

-

浏览量:2727次2020-10-22 13:36:24

-

浏览量:2855次2022-02-17 09:00:18

-

浏览量:984次2023-02-20 11:50:48

-

浏览量:518次2023-09-18 13:50:13

-

浏览量:4487次2019-10-11 09:59:54

-

浏览量:3614次2020-12-07 10:17:35

-

浏览量:3073次2020-12-24 10:21:10

-

浏览量:4439次2020-07-23 14:06:53

-

浏览量:3079次2019-10-25 17:18:33

-

浏览量:5807次2021-04-07 09:53:09

-

浏览量:24920次2022-03-17 09:00:48

-

浏览量:2811次2020-09-25 11:03:02

-

浏览量:1168次2023-03-28 15:50:07

-

浏览量:2332次2022-01-06 09:00:13

-

浏览量:4930次2022-03-29 09:00:11

-

浏览量:3542次2020-09-18 09:41:35

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

A-小鲸鱼

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友