让PCB Layout工程师相见恨晚的一些Allegro实战技巧

让PCB Layout工程师相见恨晚的一些Allegro实战技巧

1、Allegro封装原点修改

打开 dra文件后 在菜单栏 setup - change drawing origin

在命令栏输入 新的参考点位置 如想更改新坐标位置为 1,2 。输入 x 1 2

2、Allegro封装引脚编号修改

1)打开dra文件在find里面 off all 然后只点击text

2)点击需要更改的焊盘

3)菜单栏edit - text

4)弹出窗口修改即可

3、Allegro对齐操作

在placement edit模式下,选中元件,右键对齐即可。

4、Allegro走线居中技巧

双击两个pin后,直接的走线会居中。

5、Allegro快速删除dangling线

route——Gloss—–parameters

弹出选项窗口点 line smoothing 这一任务项,然后ok,然后点gloss即可消除dangling线。

6、Allegro颜色设置的导入与导出

导出:file->export->paremeter,选color

导入:file->import->paremete

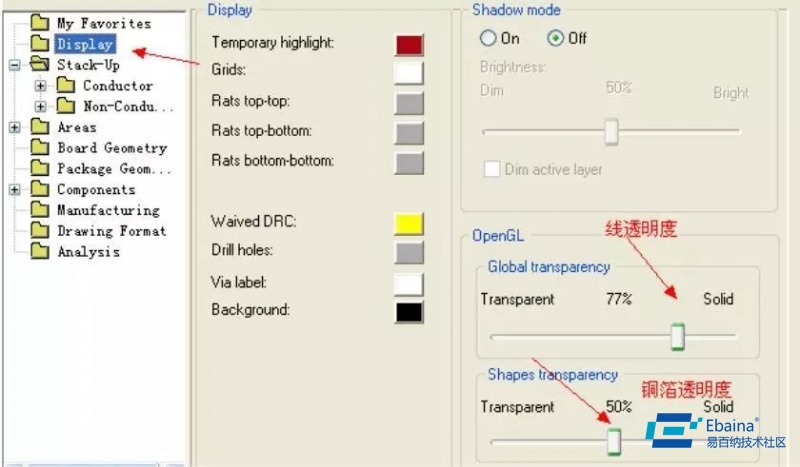

7、Allegro原色透明度设置

display->colour/visibility->display->OpenGL->Global transparency->transparent

8、Allegro如何关闭铺铜(覆铜)shape的显示

Allegro的shape 默认显示模式是通过 菜单 “Setup” -> “User Preferences…” ,然后在弹出的 “ User Preferences Editor” 用户配置窗口中选择 “Display” 选项下的 “shape_fill”, 勾选对应的选项即可实现禁止铺铜显示还是显示铺铜边框功能。

9、Allegro快速隐藏电源/地网络飞线(鼠线)

Cadence Allegro菜单栏”Edit->Net Properties…”,然后会弹出”Allegro Constraint Manager”对话框(即我们常说的约束规则管理器对话框),并会自动切换至“Properties”选项卡,我们在节点“Net->General Properties”下搜索对应的网络,如“GND、VCC-3V”,在对应的“Not Rat”列设置为“On”状态,即可隐藏对应的飞线啦。如果要取消隐藏,则选择“Clear”。

10、Allegro布线时添加过孔

1)在放置过孔前先要进行简单的设置。

在菜单栏Setup->Constraints->physical

出来的列表里面找到vias 点击出现一个对话框在对话框中选择需要的过孔。(类型比较多可以在下面过滤器输入v)

选择好过孔后关闭即可。

当然还有很多约束在这里设置,比如多大的线宽对应多大的过孔.

2)使用过孔:

在布线的时候双击左键即可添加过孔,或者点击右键。*

硬件工程师还需要了解的一些PCB设计技巧:

一、在进行高速多层PCB设计时,关于电阻电容等器件的封装的选择的,主要依据是什么?常用那些封装,能否举几个例子。

答:0402是手机常用;0603是一般高速信号的模块常用;依据是封装越小寄生参数越小,当然不同厂家的相同封装在高频性能上有很大差异。建议在关键的位置使用高频专用元件。

二、多层板布局时需要注意哪些事项?

答:多层板布局时,因为电源和地层在内层,要注意不要有悬浮的地平面或电源平面,另外要确保打到地上的过孔确实连到了地平面上,最后是要为一些重要的信号加一些测试点,方便调试的时候进行测量。

三、通孔和盲孔对信号的差异影响有多大?应用的原则是什么?

答:采用盲孔或埋孔是提高多层板密度、减少层数和板面尺寸的有效方法,并大大减少了镀覆通孔的数量。但相比较而言,通孔在工艺上好实现,成本较低,所以一般设计中都使用通孔。

四、在设计PCB 时,如何考虑电磁兼容性 EMC/EMI,具体需要考虑哪些方面?采取哪些措施?

答:好的 EMI/EMC 设计必须一开始布局时就要考虑到器件的位置, PCB 叠层的安排,重要联机的走法,器件的选择等。例如时钟产生器的位置尽量不要靠近对外的连接器,高速信号尽量走内层并注意特性阻抗匹配与参考层的连续以减少反射,器件所推的信号之斜率(slew rate)尽量小以减低高频成分,选择去耦合(decoupling/bypass)电容时注意其频率响应是否符合需求以降低电源层噪声。另外,注意高频信号电流之回流路径使其回路面积尽量小(也就是回路阻抗 loop impedance 尽量小)以减少辐射, 还可以用分割地层的方式以控制高频噪声的范围,最后,适当的选择PCB 与外壳的接地点(chassis ground)。

五、高速 PCB,布线过程中过孔的避让如何处理,有什么好的建议?

答:高速 PCB,最好少打过孔,通过增加信号层来解决需要增加过孔的需求。

六、在即有模拟电路又有数字电路的电路中,PCB 板设计时如何避免互相干扰问题?

答:模拟电路如果匹配合理辐射很小,一般是被干扰。干扰源来自器件、电源、空间和 PCB;数字电路由于频率分量很多,所以肯定是干扰源。解决方法一般是,合理器件的布局、电源退偶、PCB 分层,如果干扰特点大或者模拟部分非常敏感,可以考虑用屏蔽罩 。

七、怎样判断PCB板设计时需要多少层?

答:从走线密度、BGA和信号3方面考虑:

-

走线密度

一般来说,PCB先布局,再来评估板子的层数;布局完后,就可以看到板子的信号流向,走线顺不顺(考虑交叉线),需要几个走线层。评估重点在飞线最密集的区域,因为最密集区域的走线理顺,其他稀松的区域就easy了; -

BGA:

当有PCB上BGA时候,评估重点在于BGA的深度(就是焊盘至中间焊盘(一般为电源或者地的焊盘)的个数),BGA焊盘的间距在0.65mm以上的时候,两个深度的焊盘走一层信号线; -

信号考虑:

基于信号质量的考虑,都需要添加地层(屏蔽笼子),进行电磁干扰屏蔽,增加回流路径。比如一般来说可以toplayer-signal1-signal2-bottom,但是为了得到更好的、更加稳定的信号,可以设计成toplayer-GND-signal1-signal2-PWM-bottom(但一般都不会这样,因为成本原因)。

- 分享

- 举报

暂无数据

暂无数据-

浏览量:2605次2020-06-08 10:45:30

-

浏览量:1775次2019-11-07 08:47:06

-

浏览量:2415次2019-07-22 10:01:27

-

浏览量:626次2023-08-25 10:27:43

-

浏览量:2674次2019-11-23 08:47:35

-

浏览量:6444次2020-12-20 20:54:26

-

浏览量:2023次2020-06-11 09:19:07

-

浏览量:1722次2020-06-18 11:07:49

-

浏览量:6045次2022-03-10 13:42:49

-

浏览量:3460次2020-08-17 12:21:14

-

浏览量:1693次2019-11-15 08:58:58

-

浏览量:2182次2019-12-10 17:46:29

-

浏览量:2294次2018-12-19 13:21:52

-

浏览量:4722次2021-11-20 15:17:49

-

浏览量:3964次2019-05-23 09:30:53

-

浏览量:4948次2022-03-29 09:00:11

-

浏览量:2753次2022-11-10 10:02:57

-

浏览量:1135次2023-04-19 09:11:57

-

浏览量:1815次2020-05-06 09:55:45

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

yw-gao

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友