3D NAND闪存制造所面临的硅晶圆斜面缺陷挑战和解决方案

随着芯片尺寸不断缩小,3D NAND闪存的工艺整合复杂度越来越大,由于堆栈沉积层数增加、晶圆中心到边缘的厚度差异增大等原因,其可能产生的缺陷也越来越多。目前,业内人士正在尝试降低晶圆边缘的缺陷密度,以提高晶圆的整体良率。为了提高良率,常见的晶圆斜面缺陷,例如剥落(或分层)、颗粒污染、电弧和微屏蔽等,是工程师关注的重点。

今天,泛林集团软件应用工程师Pradeep Nanja将详细说明上述缺陷,并探讨避免这些缺陷产生的方法。

原文链接:https://www.coventor.com/blog/silicon-wafer-bevel-defects-during-3d-nand-flash-manufacturing/

斜 面

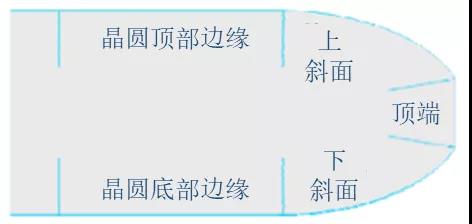

从向外2-3毫米处到晶圆边缘,有五个区域需要注意,包括晶圆顶部边缘、上斜面、顶端、下斜面和晶圆底部边缘。

图1:晶圆的有源区域或图案化区域可被划分为晶圆顶部边缘、上斜面、顶端、下斜面和晶圆底部边缘

制造标准要求对斜面区域进行抛光,以防止晶圆开裂和龟裂。在晶圆的平面和曲面之间的边缘区域,沉积的材料厚度不均匀,刻蚀速率也不尽相同。在刻蚀过程中,部分材料可能会在边缘位置被误移除,一些残留的颗粒或刻蚀聚合物也可能会落回晶圆的斜面或背面,这些颗粒和材料的堆积会导致晶圆剥落或分层,从而导致良率下降。

缺 陷 类 型

1、剥落(或分层)或颗粒缺陷:

在半导体制造工艺中,可能发生多种剥落或颗粒污染问题。在半导体制造过程中沉积的薄膜,会环绕在其边缘、斜面和顶端。而随后发生的干法刻蚀不是各向同性的,可以去除边缘上的部分沉积,但不能完全去除斜面或顶端附近的沉积。因此,剩余的堆叠薄膜会受到界面应力影响,从而无法有效粘附。在加热和冷却过程中,随着材料性能发生变化,退火步骤会导致薄膜的附着力降低,产生气泡,这些气泡在热膨胀后会继续变大。如果气泡在晶圆搬运期间破裂,便会形成额外的颗粒。湿法刻蚀工艺也会侵蚀晶圆边缘的薄表面,导致分层,进而产生更多的颗粒。由于这些颗粒可能会落在晶圆中心,造成良率损失增加,所以这是一个十分严重的缺陷。此外,3D NAND同样可能发生剥落,尤其是在存储器孔和阶梯状图形这些需要很厚的碳沉积的结构中,很有可能发生断裂和剥落。

2、电弧损伤:

电弧是气体电击穿产生的长时间放电现象。有一些工艺步骤需要反应离子刻蚀(RIE)和钨填充来产生电弧。而在反应离子刻蚀过程中,等离子体的电弧或放电问题尤为明显。在实施高深宽比反应离子刻蚀期间,低介电绝缘层中的电荷分布不均匀会造成电弧损伤。金属线是通向介质绝缘层带电区域的接地通路,而电弧损伤往往就发生在金属线附近。由于未完全去除残余颗粒,晶圆边缘会形成多层不同厚度的薄层间介质(ILD)、金属阻挡层(氮化钛)和导体薄膜(钨)。晶圆的各个位置由不同的材料制成,而这些残留的颗粒会在晶圆的不同材料之间形成多余的分界面,导致金属界面上产生电荷积聚,而金属可能在这些位置发生爆炸性蒸发。这种电荷积聚会导致金属颗粒从斜面区域喷射到晶圆的有源区域,造成不同类型的短路,严重影响良率。因此,金属沉积后需要进行适当的斜面刻蚀,以防止在反应离子刻蚀期间可能会发生破坏性电弧。此外,由于3D NAND使用的碳硬模是导电的,也是潜在的电弧源,因此也应该被去除。

3、微掩模或针状缺陷:

在高深宽比刻蚀过程中,例如在生产DRAM、NAND和功率器件时,可能出现微掩模或针状缺陷。3D NAND闪存的扩展加剧了这一缺陷。如果刻蚀材料在刻蚀期间于斜面位置处曝光,这些缺陷便会出现在斜面区域。在悬浮栅级OPOP(Oxide-Poly Si-Oxide-Poly Si)首次集成期间,存储器孔刻蚀对衬底不具有选择性,在刻蚀存储器孔和狭缝时,斜面可能出现严重的微掩模。在电荷撷取层ONON(Oxide-Nitride-Oxide-Nitride)替换栅极集成期间,存储器孔和狭缝刻蚀对硅衬底具有选择性。可以通过精细操作斜面刻蚀步骤来减轻斜面上的微掩模,避免其出现在氮氧化层。在ONON集成过程中,氮化物被去除,随后被钨替换。这种氮化物去除步骤可能会由于湿法腐蚀在斜面产生缺陷,尤其是当之前的高深宽比刻蚀步骤已在该区域形成微掩模的情况下。

斜 面 刻 蚀 工 艺

斜面刻蚀工艺用于去除晶圆边缘任何类型的薄膜,无论是介电薄膜、金属薄膜还是有机材料薄膜都可被去除。在此过程中,晶圆被夹在顶板和底板之间,因此晶圆边缘是其唯一外露的部分。这可以确保只有晶圆边缘部分被刻蚀。

图2:前侧和后侧暴露在外,即将被刻蚀的斜角和边缘区域

在斜面刻蚀过程中,氮气从晶圆中心流向边缘,防止颗粒被推到晶圆中心,污染晶圆,降低良率。斜面刻蚀的定位至关重要,因为任何错误都可能导致晶圆厚薄不均。通过预防剥落、电弧和微掩模问题,斜面刻蚀可以减少晶圆边缘出现缺陷的几率。

结 论

随着芯片尺寸的减小和复杂度的增加,减少边缘缺陷成为提高良率的要点之一。了解剥落、电弧损伤和微掩模等边缘缺陷问题对于提高晶圆良率至关重要。通过在工艺流程的特定环节添加斜面刻蚀和斜面清洗工艺,可以有效减少这些缺陷。斜面刻蚀和斜面清洁工艺将在未来的技术节点上发挥关键作用,随着系统集成的挑战不断增加,这些工艺也会被更加广泛地采用。

声明: 本文来自泛林半导体设备技术 ,目的在于信息传递,观点仅代表作者本人,不代表易百纳立场。如有侵权或其他问题,请联系我们。

- 分享

- 举报

暂无数据

暂无数据-

浏览量:3939次2020-11-11 09:50:43

-

浏览量:2110次2019-09-20 09:15:55

-

浏览量:2566次2020-07-09 13:39:17

-

浏览量:1008次2023-04-24 10:20:18

-

浏览量:4555次2020-11-12 14:15:40

-

浏览量:2899次2020-10-09 13:49:17

-

浏览量:4424次2020-07-23 14:06:53

-

浏览量:1840次2020-09-22 12:14:25

-

2020-12-01 11:13:10

-

浏览量:3672次2022-09-08 10:56:12

-

浏览量:1628次2020-06-11 14:16:13

-

浏览量:1638次2019-06-28 10:38:48

-

浏览量:3665次2020-11-19 10:01:40

-

浏览量:3072次2019-10-25 17:18:33

-

浏览量:24814次2022-03-17 09:00:48

-

浏览量:2638次2019-07-15 10:29:52

-

浏览量:3702次2020-10-16 10:57:17

-

浏览量:3078次2020-12-12 09:53:13

-

浏览量:2934次2020-10-23 17:33:33

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

A-小鲸鱼

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友