白皮书:如何使用FPGA来设计智能网卡以提高服务器的计算能力

本文前一部分介绍了目前智能网卡设计所采用的三种形式,即基于包含多个CPU内核的ASIC的多核智能网卡、基于现场可编程门阵列(FPGA)的智能网卡、以及将硬件可编程FPGA与ASIC网络控制器相结合的FPGA增强型智能网卡。今天我们将继续发布“如何使用FPGA来设计智能网卡(SmartNIC)以提高服务器的计算能力”一文的第二部分。

一步一步地构建智能网卡

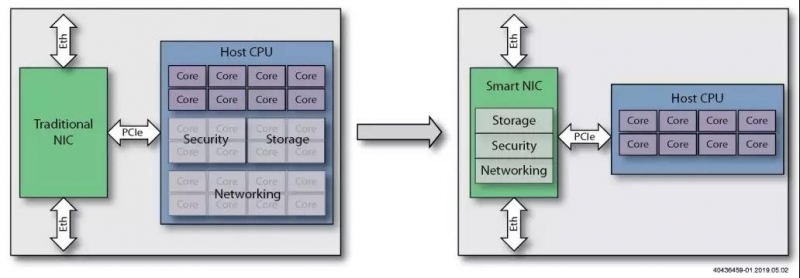

智能网卡被用于不同的部署中,包括存储、安全和网络处理。如下图所示,最终目标是实现消耗更少处理器内核的解决方案,同时以更低的成本提供更高的性能。

智能网卡的定义是广泛的,包括一个大型的功能层级结构,所有这些功能都建立在一个基本的网卡基础之上。示例1到13说明了可以添加到网卡的处理元素,以创建功能更加强大的智能网卡。当使用某种形式的FPGA来实现智能网卡时,可以根据需要轻松添加或删除这些功能。基于FPGA的智能网卡和FPGA增强型智能网卡的实现还允许对每种任务加速功能进行简便的远程修改或改进,即使智能网卡已经安装在数据中心服务器上之后也可以进行。

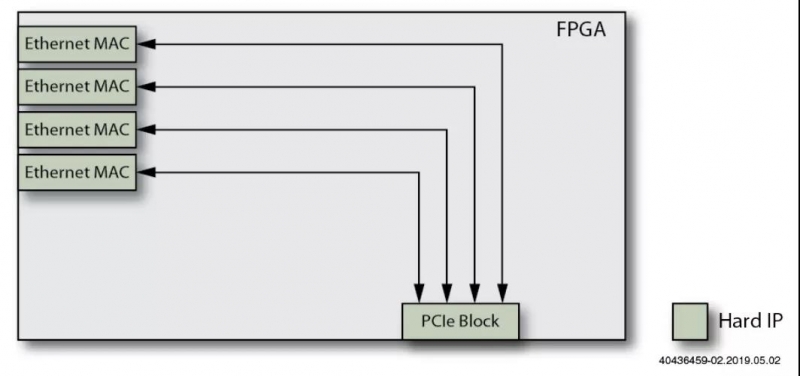

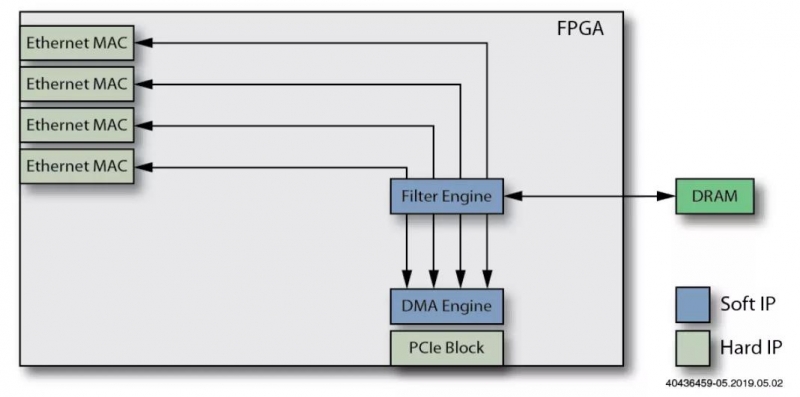

示例1展示了一个基本型网卡的基础,它采用多个以太网MAC和一个用于主处理器接口的PCIe块。主处理器随后必须处理所有以太网通信。

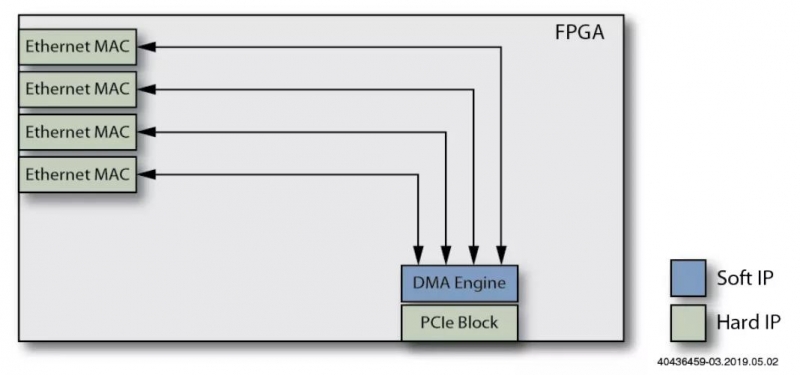

示例2将DMA引擎添加到基本型网卡中,通过允许网卡在以太网MAC和服务器内存之间移动以太网通信,而无需服务器CPU的大量干预,从而减少了主处理器的工作负载。

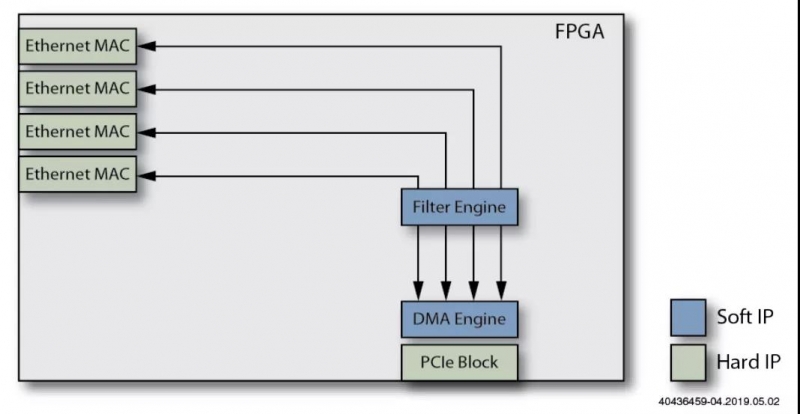

示例3添加一个过滤引擎,它通过阻止无需处理器注意的数据包,进一步减少主处理器的任务负载。

示例4将外部DRAM添加到过滤引擎,这显著增加了智能网卡上可用于过滤的规则数量。有了足够的外部内存,智能网卡可以管理数百万条规则。

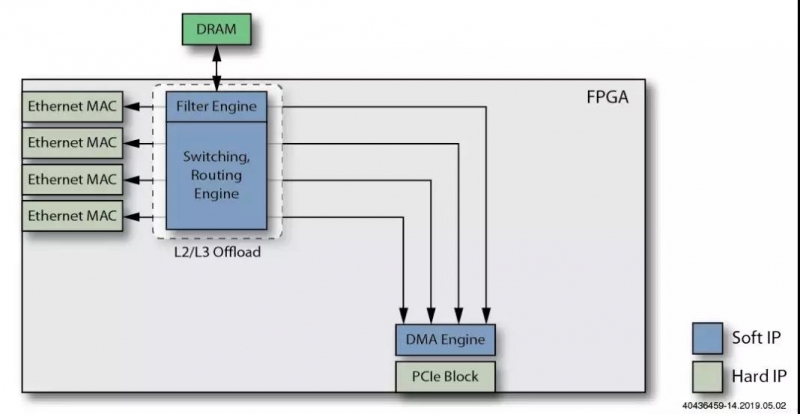

示例5添加了L2/L3卸载引擎,该引擎可以通过处理智能网卡的以太网端口之间的低层交换和路由,进一步减少主处理器的工作负载。为了有效,L2/L3卸载引擎将需要大量外部DRAM来缓冲网络数据包。

注意

智能网卡FPGA或ASIC与外部DRAM之间的接口必须满足正被交换的以太网通信带宽要求。

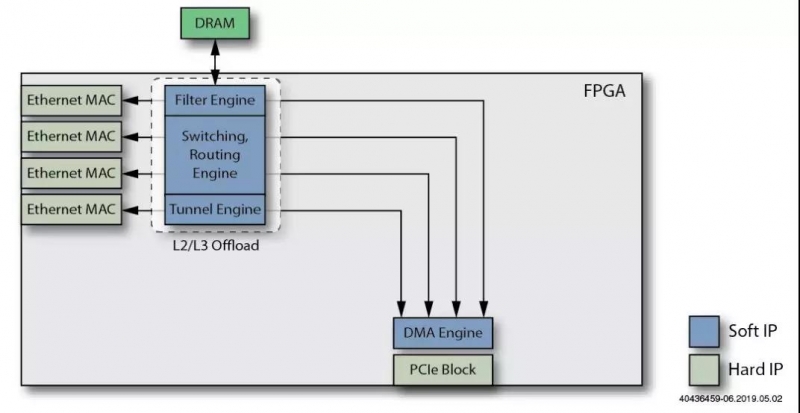

示例6添加了一个隧道引擎,以允许智能网卡卸载各种隧道封包,并进一步减轻处理器的周期密集型隧道性需求。

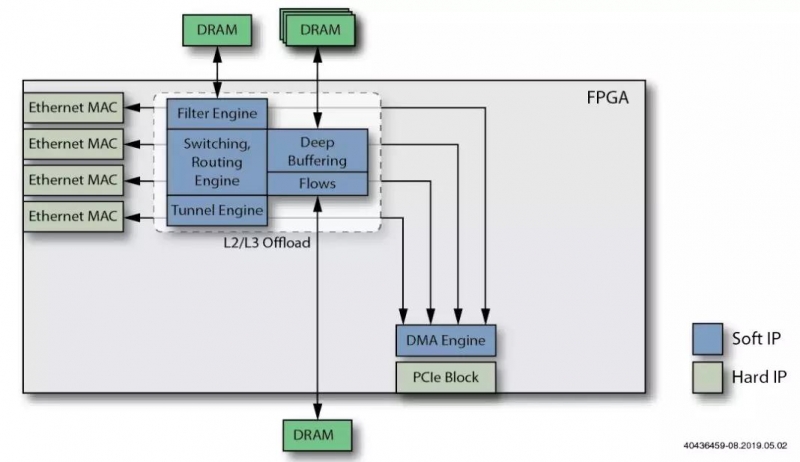

示例7添加快速外部存储,以允许智能网卡对传入的网络数据包进行深度缓冲,从而实现了线速数据包交换和具有多个队列的分层QoS调度。

示例8添加一个具有自己的DRAM缓冲的流引擎,以使智能网卡的路由引擎能够处理数百万个路由表条目。流引擎有助于卸载网络地址转换/协议地址转换(NAT / PAT)操作的负担。

声明: 本文来自Achronix,目的在于信息传递,观点仅代表作者本人,不代表易百纳立场。如有侵权或其他问题,请联系我们。

迎国庆,送好礼

- 分享

- 举报

暂无数据

暂无数据-

浏览量:4248次2020-12-03 13:59:05

-

浏览量:2354次2018-10-23 14:05:21

-

浏览量:4316次2021-04-27 11:10:24

-

浏览量:2730次2022-01-09 09:00:19

-

浏览量:3636次2020-11-23 10:42:27

-

浏览量:2084次2021-12-13 15:21:54

-

浏览量:6456次2021-01-11 14:14:40

-

浏览量:2940次2022-03-13 09:00:25

-

浏览量:4789次2021-03-09 16:10:37

-

浏览量:3388次2019-11-20 08:51:17

-

浏览量:1818次2020-01-07 10:22:02

-

浏览量:11609次2021-03-20 13:22:58

-

浏览量:3541次2020-10-26 10:42:02

-

浏览量:1307次2023-08-21 11:47:40

-

浏览量:14829次2018-12-27 13:16:45

-

浏览量:2576次2020-07-15 18:52:03

-

浏览量:3730次2020-08-13 14:29:28

-

浏览量:2504次2020-07-10 18:04:44

-

浏览量:1841次2023-06-07 14:32:02

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

tomato

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友