4种端接方法,教你完美解决信号端接困惑

时钟信号衰减会增加抖动,因此对驱动器输出的端接很重要。为了避免抖动和时钟质量降低的不利影响,需要使用恰当的信号端接方法。

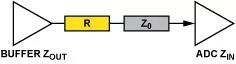

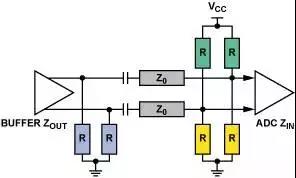

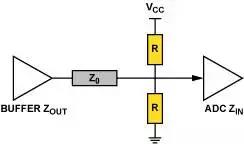

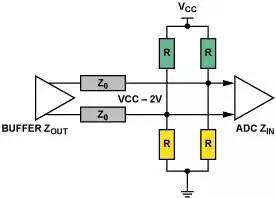

Z0是传输线的阻抗;

ZOUT 是驱动器的输出阻抗,

ZIN 是接收器的输入阻抗。

PS:这里仅显示CMOS和PECL/LVPECL电路。

串行端接

实际上,因为阻抗会随频率动态变化,难以达到阻抗匹配,所以缓冲器输出端可以省去电阻(R)。

*优势:

低功耗解决方案(没有对地的吸电流)

很容易计算R的值 R (Z0 – ZOUT).

*弱点:

上升/下降时间受RC电路的影响,增加抖动

只对低频信号有效

*备注:

CMOS驱动器

不适合高频时钟CMOS drivers信号

适合低频时钟信号和非常短的走线

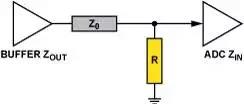

下拉电阻

*CMOS*

优势:非常简单(R = Z0)

弱点:高功耗

备注:**不推荐

*LVPECL

*优势:*

简单的3电阻解决方案。

就节能而言稍好一点,相对于4电阻端接来说节省一个电阻。

备注:**推荐。端接电阻尽可能靠近PECL接收器放置。

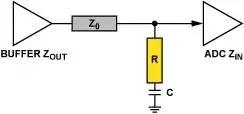

交流端接

*CMOS*

优势:**没有直流功耗。

*备注:为避免较高功耗,C应该很小,但也不能太小而导致吸电流。

*LVPECL

*优势:*交流耦合允许调整偏置电压。避免电路两端之间的能量流动。

弱点:**交流耦合只推荐用于平衡信号(50%占空比的时钟信号)。

*备注:交流耦合电容的ESR值和容值应该很低。

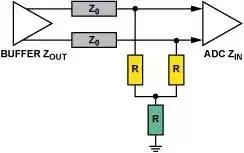

电阻桥

*CMOS*

优势:**功耗实现合理的权衡取舍。

*弱点:单端时钟用两个器件。

*LVPECL*

弱点:**差分输出逻辑用4个外部器件。

*备注:3.3V LVPECL驱动器广泛应用端接。

声明: 本文来自亚德诺半导体,目的在于信息传递,观点仅代表作者本人,不代表易百纳立场。如有侵权或其他问题,请联系我们。

- 分享

- 举报

暂无数据

暂无数据-

浏览量:3675次2019-11-18 11:15:10

-

浏览量:1825次2020-06-05 11:53:54

-

浏览量:2393次2019-11-11 10:43:40

-

浏览量:1690次2023-04-19 09:13:30

-

浏览量:2011次2020-03-14 10:25:11

-

浏览量:3631次2021-03-31 17:16:31

-

浏览量:3414次2023-04-20 13:49:28

-

浏览量:2172次2020-08-05 20:33:33

-

浏览量:3296次2019-09-17 17:30:56

-

浏览量:2810次2020-06-08 10:45:30

-

浏览量:2870次2019-05-07 10:32:49

-

浏览量:7856次2020-09-10 09:46:52

-

浏览量:4626次2020-11-14 09:41:56

-

浏览量:3546次2020-05-07 19:02:31

-

浏览量:2580次2019-10-31 17:27:45

-

浏览量:1380次2020-10-15 14:47:39

-

浏览量:2316次2018-04-16 11:35:00

-

浏览量:6869次2021-01-30 01:09:16

-

浏览量:1922次2022-12-14 13:44:12

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

A-小鲸鱼

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友